You are looking for information, articles, knowledge about the topic nail salons open on sunday near me capacitance voltage 측정 on Google, you do not find the information you need! Here are the best content compiled and compiled by the https://chewathai27.com/to team, along with other related topics such as: capacitance voltage 측정 Capacitance Voltage 측정 원리, 반도체 CV 측정, CV 측정장비, CV 측정 방법, CV 측정 이유, Capacitance-voltage curve, CV curve 해석, Capacitor cv curve

Oxidation, C-V 측정법, LFCV, HFCV : 네이버 블로그

- Article author: m.blog.naver.com

- Reviews from users: 18392

Ratings

- Top rated: 4.1

- Lowest rated: 1

- Summary of article content: Articles about Oxidation, C-V 측정법, LFCV, HFCV : 네이버 블로그 Oxation의 두께를 측정하는 방법중의 하나인 C-V 측정법에 대해 포스팅해볼게요. . 제 나름대로의 생각은. Oxation을 진행하고나면, … …

- Most searched keywords: Whether you are looking for Oxidation, C-V 측정법, LFCV, HFCV : 네이버 블로그 Oxation의 두께를 측정하는 방법중의 하나인 C-V 측정법에 대해 포스팅해볼게요. . 제 나름대로의 생각은. Oxation을 진행하고나면, …

- Table of Contents:

카테고리 이동

_

이 블로그

반도체

카테고리 글

카테고리

이 블로그

반도체

카테고리 글

반도체(14) MOS 커패시터, MOS Capacitor

- Article author: luv-n-interest.tistory.com

- Reviews from users: 16648

Ratings

- Top rated: 3.9

- Lowest rated: 1

- Summary of article content: Articles about 반도체(14) MOS 커패시터, MOS Capacitor 커패시터의 C-V 특성부터 알아보도록 하자, C-V 측정은 DC 바이어스 전압 Vg와 정현파 소신호(Hz~MHz)를 MOS 커패시터에 인가하여 AC 전류계로 용량성 … …

- Most searched keywords: Whether you are looking for 반도체(14) MOS 커패시터, MOS Capacitor 커패시터의 C-V 특성부터 알아보도록 하자, C-V 측정은 DC 바이어스 전압 Vg와 정현파 소신호(Hz~MHz)를 MOS 커패시터에 인가하여 AC 전류계로 용량성 … 커패시터의 C-V 특성부터 알아보도록 하자, C-V 측정은 DC 바이어스 전압 Vg와 정현파 소신호(Hz~MHz)를 MOS 커패시터에 인가하여 AC 전류계로 용량성 전류를 측정한다. 이 때 커패시턴스는 다음과 같이 구할 수..기술: C++, C#, Unity, Unreal, DX ++ devops k8s

관심분야: 새로운 컨텐츠를 구현하는게 제일 재밌는 것 이라고 생각하고 있으며 이미 있는 것에 대해 최적화 또는 리팩토링하는데에 관심이 있습니다(엔진 튜닝 또는 커스터마이징) 하지만 개발은 항상 힘이 듭니다. 그래서 포기하고 싶을 때도 많지만 내일 또다시 시도해봅니다.

요즘엔 새로운 것에 눈을 떴습니다. - Table of Contents:

반도체(14) MOS 커패시터 MOS Capacitor

티스토리툴바

RISS 원문다운로드

- Article author: m.riss.kr

- Reviews from users: 47720

Ratings

- Top rated: 4.3

- Lowest rated: 1

- Summary of article content: Articles about RISS 원문다운로드 본 논문은 MOS 커패시터의 C-V 측정 특성을 설명하고 C-V 곡선이 평형상태에. 도달하지 않고도 깊은 공핍(Deep Depletion) 상태에서의 데이타를 이용해서 플랫. …

- Most searched keywords: Whether you are looking for RISS 원문다운로드 본 논문은 MOS 커패시터의 C-V 측정 특성을 설명하고 C-V 곡선이 평형상태에. 도달하지 않고도 깊은 공핍(Deep Depletion) 상태에서의 데이타를 이용해서 플랫.

- Table of Contents:

capacitance voltage 측정

- Article author: www.koreascience.or.kr

- Reviews from users: 34363

Ratings

- Top rated: 3.2

- Lowest rated: 1

- Summary of article content: Articles about capacitance voltage 측정 semiconductor field-effect transistor)의 capacitance. 값은 매우 작아지고 있기 때문에 C-V (capacitance voltage) 측정환경을 구축할 때 주의를 기울여야 한다. …

- Most searched keywords: Whether you are looking for capacitance voltage 측정 semiconductor field-effect transistor)의 capacitance. 값은 매우 작아지고 있기 때문에 C-V (capacitance voltage) 측정환경을 구축할 때 주의를 기울여야 한다.

- Table of Contents:

MOSFET CAPACITANCE 구성 및 측정(1)

- Article author: zzoonijjoons.tistory.com

- Reviews from users: 35159

Ratings

- Top rated: 4.1

- Lowest rated: 1

- Summary of article content: Articles about MOSFET CAPACITANCE 구성 및 측정(1) 저렇게 큰 사이즈는 Overlap 및 Fringing capacitance가 OXIDE capacitance에 묻히기 때문이죠. 이것을 측정해보면 여러분들이 알고 있는 CV 특성커브 … …

- Most searched keywords: Whether you are looking for MOSFET CAPACITANCE 구성 및 측정(1) 저렇게 큰 사이즈는 Overlap 및 Fringing capacitance가 OXIDE capacitance에 묻히기 때문이죠. 이것을 측정해보면 여러분들이 알고 있는 CV 특성커브 … MOSFET CAPACITANCE는 어떤 책에서는 Intrinsic/Extrinsic CAPACITANCE로 구분하기도 하고, Gate/Junction/Overlap/Fringing CAPACITANCE로 나누기도 합니다. 두 개를 매칭해보면 다음과 같습니다.(물론 절대적으..

- Table of Contents:

날아라팡’s 반도체 아카이브

MOSFET CAPACITANCE 구성 및 측정(1) 본문

티스토리툴바

capacitance voltage 측정

- Article author: link.springer.com

- Reviews from users: 33184

Ratings

- Top rated: 3.9

- Lowest rated: 1

- Summary of article content: Articles about capacitance voltage 측정 These may be described by additional elements in the equivalent circuit of the measurement, as shown in Fig.A.6. Parasitic elements which may be present include … …

- Most searched keywords: Whether you are looking for capacitance voltage 측정 These may be described by additional elements in the equivalent circuit of the measurement, as shown in Fig.A.6. Parasitic elements which may be present include …

- Table of Contents:

16강. MOS Capacitor C-V 특성그래프

- Article author: e-funny.tistory.com

- Reviews from users: 3023

Ratings

- Top rated: 4.7

- Lowest rated: 1

- Summary of article content: Articles about 16강. MOS Capacitor C-V 특성그래프 이번에는 지난 포스팅에서 다뤘던 MOS Capacitor의 각 영역들에서 커패시터 값을 알아보겠습니다. MOS Capacitor는 게이트전압 Vg에 따라서 Accumulation(축적), … …

- Most searched keywords: Whether you are looking for 16강. MOS Capacitor C-V 특성그래프 이번에는 지난 포스팅에서 다뤘던 MOS Capacitor의 각 영역들에서 커패시터 값을 알아보겠습니다. MOS Capacitor는 게이트전압 Vg에 따라서 Accumulation(축적), … 이번에는 지난 포스팅에서 다뤘던 MOS Capacitor의 각 영역들에서 커패시터 값을 알아보겠습니다. MOS Capacitor는 게이트전압 Vg에 따라서 Accumulation(축적), Depletion(공핍), Inversion(반전)영역으로 나뉩니..

- Table of Contents:

(PDF) Capacitance-Voltage Measurement | Chao Fang – Academia.edu

- Article author: www.academia.edu

- Reviews from users: 47965

Ratings

- Top rated: 3.9

- Lowest rated: 1

- Summary of article content: Articles about (PDF) Capacitance-Voltage Measurement | Chao Fang – Academia.edu Capacitance-Voltage Measurement Capacitance-voltage (CV) measurements are conventionally made using a dedicated test fixture situated within a light … …

- Most searched keywords: Whether you are looking for (PDF) Capacitance-Voltage Measurement | Chao Fang – Academia.edu Capacitance-Voltage Measurement Capacitance-voltage (CV) measurements are conventionally made using a dedicated test fixture situated within a light … Capacitance-Voltage Measurement

- Table of Contents:

See more articles in the same category here: https://chewathai27.com/to/blog.

Oxidation, C-V 측정법, LFCV, HFCV

안녕하세요ㅎㅎ

저번부터 하루에 전공공부를 꼭 하겠다는 마음가짐을 가지고

공정쪽을 보고있는데, 사실 말이 공정이지 반도체소자와 전자회로를 전반적으로 이해해야해요

쨋든 그중에서 Oxidation을 한 후,

Oxidation의 두께를 측정하는 방법중의 하나인 C-V 측정법에 대해 포스팅해볼게요

제 나름대로의 생각은

Oxidation을 진행하고나면, 당연히 실질적인 두께를 알 수가 없겠죠

왜냐면 늘 이상과 현실은 다르니까!

그래서 Cap값을 측정하면 Cap은 dQ/dV = 유전율 * ( 면적 / 두께 ) 이고

면적, 유전율은 상수이니까 두께를 알 수 있겠죠

이게 C-V 측정법의 의의 인듯합니다.

그래서 MOS를 동작시키기 위한 DC값과 해당 MOS에 dQ를 볼 수 있는 AC값을 함께 넣어줍니다.

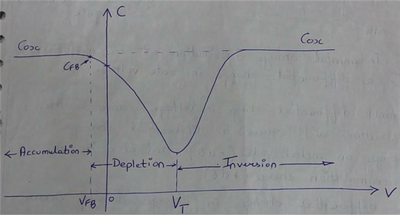

먼저 기본적인 C-V 그래프에 대해 이해하고

측정법과 관련시켜 넘어가보겠습니다

그림은 그냥 구글링해서 누가 필기한걸 가져온거라 허접한데

그래서 원래는 아래와 같이 이상적인 그래프를 가진다고해요

해당 그래프는 n-채널, p 기판인 MOS에 대한 그래프에요

아시다시피 Accumulation은 딱히 변화가 없는 상태이죠

Depeletion은 이제 Vg값이 Vt보단 작지만 그래도 어느정도 양의 전압이 가해지기 때문에

채널 형성전에 공핍층이 만들어지는 시기이구요

마지막 Inversion이 바로 우리가 원하는 채널이 형성된 상태이죠

그래서 세 경우에 대해서 Oxidation의 두께와의 상관관계를 볼겁니다.

먼저 Accumulation에서, n-채널 형성이 목적이고, p 기판에 해당 측정법을 진행할 때

Q의 준위는 다음과 같이 Metal의 경우엔 -Q, Oxidation은 절연체니까 0,

Silicon의 경우엔 아직 채널이 형성되지 않았고, 그냥 p 기판이니까 +Q겠죠

그래서 아래 그림과 같습니다. -dQ의 경우엔 저희가 DC와 함께 AC(교류 전압)을 인가하면서 생기는 변화에요

이 경우엔 C 값이 단순하게 Oxidation에 의해서만 영향을 받구요 (즉 단순히 Oxide Capacitance)

그 식은 아래와 같습니다.

그리고 당연한 이야기지만, 유전율, 면적, Oxidation 두께 모두 일정하기 때문에

C 값이 앞서 보여드린 그래프와 같이 일정합니다.

식으로 굳이 나타내자면 이렇습니다.

그 다음으로 게이트에 어느정도의 양의 전압이 인가되는 순간,

p 기판의 정공은 밀려나고, 해당 자리는 공핍영역이 됩니다. 즉 depletion 상태가 되죠

그 경우 아래와 같은 전하양상을 띕니다.

당연히 Metal gate에 양의 전압을 인가하기 때문에 양의 +Q +dQ가 보이고

반대 쪽에는 -Q, -dQ가 보입니다.

그리고 이 경우, oxidation 외에, 공핍영역이라는 절연층이 또 생기기 때문에

(사실 공핍영역은 절연층은 아니지만… 어느정도 전하가 존재하지 않는 영역이기 때문에

Cap 값이 어쩔 수 없이 생깁니다. 그래서 depletion area를 기준으로

source, body, drain에 여러 기생 cap이 생기죠ㅎㅎ)

이 경우 Cap값은 아래와 같이 oxide와 depletion 모두를 고려해줍니다.

이 경우 Cox 값은 일정하기 때문에 Cdep에 의해 총 Cap값이 결정됩니다.

Cdep의 경우에도 유전율과 면적은 어느정도 결정되기 때문에

depletion의 두께에 따라서 Cs 값이 결정됩니다.

당연히 gate에 인가된 양의 전압이 커질수록 depletion area가 두꺼워지지만,

반도체소자에서 배웠듯이, MOS 또는 pn 공핍층엔 maximum depletion width가 있습니다.

그냥 상식적으로 생각해봐도, 절연체를 뚫고 그 아래에 있는 p 기판에

무한하게 영향을 줄 수 있진않겠죠?

그리고 depletion 상태에서 전압을 더 인가하면, 계속해서 그 영역이 늘어나는 것이 아니라

어느정도 수준에서 멈추고, 이제 전자가 끌려와 채널을 형성하게 됩니다.

그 지점이 흔히 말하는 threshold voltage, 문턱 접압이에요ㅎㅎ

쨋든! 그래서 위의 그래프에서도 보면 Vth 지점에서 Cap 값이 가장 낮아지는 것 까지

확인이 가능합니다.

그리고 마지막으로 Inversion!!

이 경우 n 채널이 형성되면서, 공핍층의 끝부분에서 눈에 띄는 전하의 움직임이 없게됩니다.

아시다시피 oxidation을 기준으로 아래 채널을 형성하면서 전하가 움직이기 때문에

결국 Cdep은 고려대상이 아니고 다시 Cox만 고려해주면 되는것이죠

아래 그래프는 이런 상황을 좀 더 잘 보여줍니다.

보시다시피, dQ값이 depeletion 영역의 끝이 아닌

Oxidation을 기준으로 일어나고있죠? 그래서 결국 C값이 다시 상승하고 앞서 구했던 Cox의 값이 됩니다.

그렇다면 이제 LFCV, HFCV에 대해서 이해해보겠습니다.

LFCV = Low Frequency CV, High Frequency CV 입니다.

즉 인가된 전압의 진동수가 느릴 때와 빠를 때의 CV를 보겠다는거죠.

생각해보면 당연한게 저희가 AC를 인가해서 AC에 의해 Cap이 변화되는 것을 측정하잖아요?

위의 경우는 모두 이상적인 경우인것이고, 실제로는 AC의 진동수까지 고려해줘야

제대로 상황을 파악할 수 있는것이죠

그래서 정확히 주파수까지 고려를해서 측정을 해보면

다음과 같이 세 가지 경우가 생깁니다.

원래 위에서 봤던, LFCV , HFCV, deep depletion

간략하게 먼저 설명하고 넘어가자면

LFCV의 경우 주파수가 꽤 느려서, 인가된 게이트 전압에 의해서 캐리어에 변화를 정확히 줄 수 있는 경우입니다.

즉 앞서 설명했듯이 dQ가 정확히 일어나는 경우인거죠

HFCV의 경우엔, 주파수가 너무 빠르기 때문에 DC값에 의해선 영향을 받지만

AC에 의한 영향을 제대로 받지 못하고, 결국 depletion 영역 상태에서 벗어나지 못한 경우입니다.

deep depletion은 그보다 더 빠르기 때문에 오히려 공핍층이 더 넓어지기만하는 최악의 경우입니다.

제 생각이지만, 아마 LFCV의 경우에만 MOS가 제대로 동작할 것이고

HFCV의 경우엔 depletion 영역의 넓이는 커지지않지만, 채널이 형성되지 못해서 제대로 동작못하고

deep depletion은 depletion의 영역만 넓어지기 때문에 제대로 동작못하는 경우라고 생각됩니다.

관련 자료를 찾아보니 HFCV의 경우 보시다시피 dQ의 변화가 depletion영역 끝에서 생기잖아요?

그러니까 채널이 엉뚱한 곳에 생기고있단 뜻이죠

그리고 이어서 생각해보면

HFCV의 경우엔 그림과 같이 dQ값이 depletion region 끝에서 생기니,

Cap 값이 depletion과 oxidation 모두에 영향을 받을 것입니다.

deep depletion의 경우엔 계속해서 공핍층이 넓어지므로,

Cap 값이 depletion과 oxidation에 의해 영향을 받으면서, 점점 낮아지는 것이구요

여기까지 설명하면 결국 앞서 보여드린 그래프에 관한 설명이 끝나내요ㅎㅎ

그 외에 Flat Voltage V_FB도 oxidation의 charge에 의해 영향을 받는다는 이야기도 나오는데…

거기까진 잘 이해가 안가기도하고

너무 가는거같아서

사실 여기까지 배우지도 않았어요 학교에선 그냥 간단히 넘어갔는데

늘 궁금하긴 했거든요 C-V 특성이 왜 저렇게 되나??

쨋든 저는 Oxidation 후에 측정법의 일종으로 C-V에 대해서 배웠지만,

거기에만 국한되는 것이 아니라

그냥 일반적인 MOS의 특성으로 이해하셔도 될 듯해요

LFCV, HFCV도 측정법이 아니라 Voltage의 진동수에 따른 특성을 말한거였네요 ㅎㅎ

이부분 책을 찾아도 잘 없는 부분이니 유용하게 참고하시면 좋겠습니다

저도 속이 시원하네요!

그럼 또 정리할 만한 부분 나오면 포스팅할게요

반도체(14) MOS 커패시터, MOS Capacitor

728×90

반응형

728×170

커패시터의 C-V 특성부터 알아보도록 하자,

C-V 측정은 DC 바이어스 전압 Vg와 정현파 소신호(Hz~MHz)를 MOS 커패시터에 인가하여 AC 전류계로 용량성 전류를 측정한다.

이 때 커패시턴스는 다음과 같이 구할 수 있다.

회로이론에서 많이 봤을 것같다.

++우리는 커패시터를 배울 때 주파수 특성도 같이 배운다.

Vg에 따라 다양한 모습을 보일거 같은 느낌이다.

실제로 그렇다

MOS 이론에서의 커패시터는 항상 소신호 커패시턴스를 의미하는데

**이러한 상태를 Quasi-static C-V 라고 한다.

++반전 전하가 AC 신호에 마치 주파수가 무한히 낮은 것처럼(정적 상태) 반응하기 때문이다. 이러한 조건을 만들기 위해서는 별도의 N형 영역과 같은 전자 공급원이 존재해야 한다.

(밑에 그림 c를 보면 된다)

축적 영역, 공핍 영역, 반전 영역 보면 알듯이 게이트 전압에 따라 다양한 모습을 보인다.

++참고로 얘는 LF(Low Frequency) 상태이다.

축적 영역 : 게이트 전압 변화(AC)에 따라, 실리콘 표면의 축적 전하의 양이 변한다.

-> 단순히 Cox의 값을 갖는 커패시터.

공핍 영역 : 공핍 영역의 경우에 캐리어는 없고, 전하를 띠는 것은 노출된 도펀트이온이다. 게이트 전압 변화에 따라, 공핍층의 폭(Wdep)가 변하게 되고, 이에 따른 전하의 변화는 공핍층의 하단부에서 나타난다.

-> Cox 와 Cdep 의 직렬 연결

++커패시터의 직렬은 저항의 병렬과 식이 같다.

반전 영역 : 게이트 전압 변화(AC)에 따라, 실리콘 표면의 반전 전하의 양이 변한다.

-> 단순히 Cox의 값을 갖는 커패시터.

그림으로 볼까??

a: 축적

b: 공핍

c: 반전 (LF)

d: 반전 (HF)

High Frequency일 때는 아직 설명 하지 않았지만 그림 보고 알아보자

고주파 C-V (HF C-V) : 전자 공급원이 존재하지 않는 경우, 반전전하는 고주파 (~MHz) AC 신호 변화에는 반응하지 못하여 DC 상태에서의 양에 머물게 된다. 대신, 충분히 많은 다수 캐리어가 공핍층 끝부분에서 반응하게 된다.

-> Cmin 에서 일정하게 유지됨.

NMOS와 PMOS에 대해서 알아보자

NMOS란 반전 영역에서 N이 모아지는

PMOS란 반전 영역에서 P가 모아지는

즉 반전 영역을 기준으로 전자, 정공 뭐가 모이느냐에 따른 이름이다.

NMOS : p-type substrate (inversion charge : N-type)

PMOS : n-type substrate (inversion charge : P-type)

평탄 밴드 전압 : NMOS는 음의 Vfb 전압, PMOS는 양의 Vfb 전압

문턱 전압 : NMOS는 양의 문턱전압, PMOS는 음의 문턱전압

반전 조건 : NMOS는 Vg >Vt , PMOS는 Vg

MOSFET CAPACITANCE 구성 및 측정(1)

MOSFET CAPACITANCE는 어떤 책에서는 Intrinsic/Extrinsic CAPACITANCE로 구분하기도 하고, Gate/Junction/Overlap/Fringing CAPACITANCE로 나누기도 합니다.

두 개를 매칭해보면 다음과 같습니다.(물론 절대적으로 아래 분류가 맞다곤 할 수 없습니다.)

Intrinsic Capacitance – Gate Capacitance

Extrinsic Capacitance – Junction/Overlap/Fringing Capacitance

아래 그림은 MOSFET node에 metal line (그림상으론 CONTACT죠)까지 연결된 그림입니다.

Cox는 MOS CAPACITOR와 동일하다고 생각하면 됩니다.

대학교 전공을 배울 때, 아쉬운 점은 MOS CAPACITOR인 Cox 외에 나머지에 대해 자세히 배우지 않는다는 사실입니다. 여러분이 흔히 아는 Logic 소자는 timing, 즉 속도가 중요하기 때문에 MOSFET Capacitor에 대한 이해가 정말 중요합니다.

위 사진은 면접을 보러가던지, 반도체 일을 하던지 반드시 머리속에 숙지하면 좋습니다.

그럼 위와 같은 MOSFET을 측정한다고 상상해보죠.

사이즈는 Width/Length = 500u×1u입니다.

이 사이즈를 그려보면 Poly gate가 엄청 큰 사각형으로 아래처럼 그려질겁니다. 업계에서는 이것을 흔히 Area pattern이라고 부릅니다.

그렇다면 패턴을 테스트하기 위해 할당받은 면적은 작은데 왜 이렇게 큰 사이즈를 탑재하여 측정할까요?

그것은 Size가 작아짐에 따라 부수적으로 붙는 영향들을 최소화하기 위함입니다. 저렇게 큰 사이즈는 Overlap 및 Fringing capacitance가 OXIDE capacitance에 묻히기 때문이죠.

이것을 측정해보면 여러분들이 알고 있는 CV 특성커브를 구할 수 있게되는 겁니다.

어라?위 사진에서 여러분이 흔히 보던 CV 특성커브와 다른 점이 없나요? INVERSION 영역을 보면 GATE 전압이 증가하면서 capacitance가 작아지고 있네요.

이것은 Poly gate depletion effect로 인해 발생하는 현상으로 반도체를 심도있게 공부한 분들은 알 수 있을겁니다. 자세한 내용은 다른 포스팅에서 다루도록 하겠습니다.

일반적으로 위와 같은 측정은 CGG 그래프라고 부르기도 합니다. 그 외에도 CGC, CGB, CGB 등등이 있죠.(뒤에서 설명하겠습니다…)

제가 포스팅 처음에 MOS Capacitance는 Oxide capacitance외에 다양한 capacitance로 구성된다고 말했죠?

SPICE MODELING 입장에선 이것을 분리하여 모델링할 필요가 생겼고 측정방법에 따라 CGG, CGB, CGC, CGD 등으로 나누게 되며, CGG=CGC+CGB입니다

CGG 등 용어 설명은 아래와 같으니 참고바랍니다.

이것을 측정하게 되면 아래처럼 측정이 될 겁니다.

이 그래프들을 겹치면 아래와 같이 보여집니다.

위 그림에서 주목할 점이 두 가지 있습니다.

1. accumulation 영역에서 cgb와 cgc간 capacitance 차이

accumulation 영역에서 cgb와 cgc간 capacitance 차이가 보이나요? 대략 350fF 차이가 나네요.

이것은 Overlap과 Fringing capacitance 값에 의한 것으로 그 비중이 커질수록 차이가 많이 나게 됩니다.

근데 제가 Area pattern을 설명하면서 overlap과 fringinf capacitance 영향이 작다고 말했던 것과 다르네요..

위 그림은 어떤 공정인지 모르겠으나 8인치 공정에서는 저렇게 차이가 나게 보이진 않습니다.

2. GATE VIAS가 0V 이하인 지점에서 CGC와 CGD 트렌드

GATE VIAS가 0V 이하인 지점에서 CGC와CGD 그래프가 평행한걸 볼 수 있습니다. 하지만 실제는 저렇게 나오지 않고 GATE BIAS가 작아질수록 값이 점점 작아집니다.

이것은 LDD Structure를 사용한 MOSFET에서 볼 수 있는 현상입니다. 이것을 “Overlap capacitance가 Gate bias dependency가 있다.”라고 합니다.(자세한건 다음 포스팅을 봐주세요.)

글이 길어지면 이해하기 힘드니 MOSFET CAPACITANCE 측정방법에 대한 설명은 다음 포스팅에 이어서 쓰도록 하겠습니다~

#출처

1. https://www.researchgate.net/figure/MOSFET-capacitances-in-subthreshold-regime_fig1_224394917

2. https://silvaco.com/examples/utmost4/section2/example11/index.html

3. https://www.nextnano.de/nextnano3/tutorial/1Dtutorial_MIS_CV.htm

So you have finished reading the capacitance voltage 측정 topic article, if you find this article useful, please share it. Thank you very much. See more: Capacitance Voltage 측정 원리, 반도체 CV 측정, CV 측정장비, CV 측정 방법, CV 측정 이유, Capacitance-voltage curve, CV curve 해석, Capacitor cv curve